الوصف

خلاصة

توجد طريقتان عامتان لحساب الخوارزميات. الطريقة الأولى هي ASIC والتي يمكنها تنفيذ الخوارزميات المطلوبة للأجهزة. تم تصنيع هذه الأنواع من المعدات لكل خوارزمية محددة ، لذا فهي سريعة وفعالة. لكن بعد بناء الدائرة ، فإنها لا تتغير. الطريقة الثانية هي استخدام المعالجات الدقيقة الأكثر مرونة. يقومون بتشغيل سلسلة من الأوامر ويمكن تغيير برامج النظام دون تغيير الأجهزة. ولكن ، باعتبارها ASIC ، فهي ليست مصممة لتطبيق معين ، لذا فهي ليست مرنة. تم تطوير الأنظمة القابلة لإعادة التكوين بطريقة تساعد على تقليل الفجوة بين الأجهزة والبرامج وأيضًا لتحقيق أداء ومرونة أعلى بكثير للبرامج والأجهزة. لذلك ، في هذا المشروع ، أولاً ، يتم تقديم نبذة تاريخية عن تطور النظام القابل لإعادة التشكيل. بعد ذلك ، يتم تقديم مفهوم إعادة التشكيل وجميع التصاميم ذات الصلة. تم تقديم تصميم FPGA القابل لإعادة التشكيل على الرقاقة. يتم تقديم ميزات تصميم لغة برمجة تعتمد على VHDL. أخيرًا ، نقدم نظام الأجهزة والبرامج الذي لديه القدرة على الطريقة القابلة لإعادة التكوين ، ويستخدم النظام معالجة متوازية قابلة لإعادة التكوين مما يزيد من الأداء.

المرجعي:

- A.Wang Lie, Wu Feng-yan “Dynamic partial reconfiguration in FPGAs,” 2009 Third International Symposium on Intelligent Information Technology Application.

- A.Trailokya Nath Sasamal, Anand Mohan, 2011 . “a specially designed transient faults injection technique at the vhdl level and modeling,” ijrras 9 (2) ● November.

- B. Maamar Touiza , Gilberto Ochoa-Ruiz, 2012. “A novel methodology for accelerating bitstream relocation in partially reconfigurable systems,” Microprocessors and Microsystems journal .

- B. Krill, A.Ahmad, 2010. “An efficient FPGA-based dynamic partial reconfiguration design flow and environment for image and signal processing IP cores,” Signal Processing: Image Communication 25.

- C.Abhishek Tiwari, 2012. “A Partial Reconfiguration based Approach for Frequency Synthesis using FPGA,” International Conference on Communication Technology and System Design 2011, Procedia Engineering 30 .

- D. Christopher T. Rathgeb, 2009. “Secure processing using dynamic partial reconfiguration,” CSIIRW ’09, April 13-15, Oak Ridge, Tennessee, USA Copyright ACM.

- K. KE˛PA, F. MORGAN, and K. Ko´Sciuszkiewicz. “Design Assurance Strategy and Toolset for Partially Reconfigurable FPGA Systems,” National University of Ireland, Universit’ at Karlsruhe Institute of Technology (KIT).

- L.Dirk Koch, Christian Beckhoff, and Jim Torresen, 2010. “Zero logic overhead integration of partially reconfigurable modules,” SBCCI’10, São Paulo, Brazil. Copyright 2010 ACM.

- L.Seema Verma. 2011. “Improvement in RSA Cryptosystem, journal of advances in information technology, VOL. 2, NO. 3.

- M.Kyprianos Papadimitriou And Apostolos Dollas, 2011. “Performance of partial reconfiguration in FPGA systems A survey and a cost model,” ACM Transactions on Reconfigurable Technology and Systems, Vol. 4, No. 4, Article 36, Publication date: December.

- .José Rodrigo Azambuja August, 30–September 2, 2011. “Using Dynamic Partial Reconfiguration to Detect SEEs in SBCCI’11, João Pessoa, Brazil. Copyright 2011 ACM.

- O.Robert S. Boyer And J Strother Moore, 2012. “Proof Checking The Rsa Public Key Encryption Algorithm1,” Mathematical Association of America is collaborating with JSTOR to digitize.

- P.Lubos Gaspar, October 2012. “Secure Extension of FPGA General Purpose Processors for Symmetric Key Cryptography with Partial Reconfiguration Capabilities,” ACM Transactions on Reconfigurable Technology and Systems, Vol. 5, No. 3, Article 16, Publication date.

- P.Ivan Gonzalez, 2012. “Virtualization of reconfigurable coprocessors in HPRC systems with multicore architecture,” Journal of Systems Architecture 58.

- R.Daniel Llamocca, Member, IEEE, and Marios Pattichis, Senior Member, IEEE, MARCH 2013. “A Dynamically Reconfigurable Pixel Processor System Based on PowerEnergy-Performance-Accuracy Optimization,” Ieee Transactions On Circuits And Systems For Video Technology, Vol. 23, No. 3.

- Z.Qianming Yang, 2013. “Accelerating thread-intensive and explicit memory management programs with dynamic partial reconfiguration,” J Supercomput.

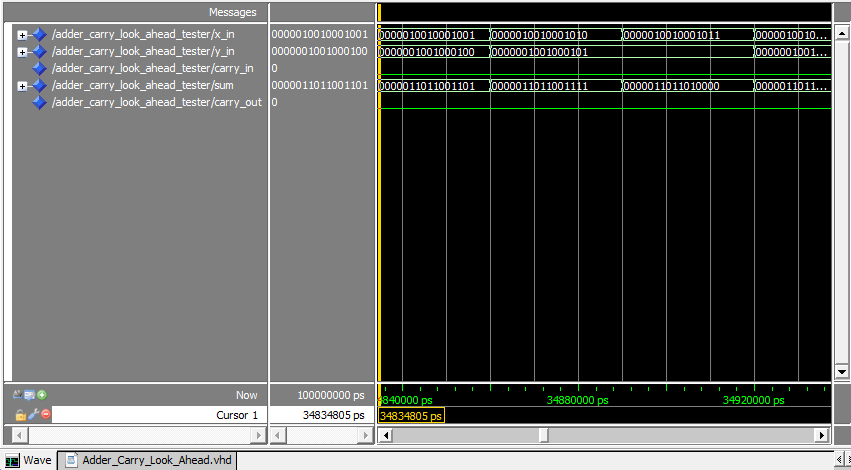

إخراج برنامج Modelsim:

الأفعى:

المضاعف:

مقسم:

ALU :

النتيجة التوليفية لبرنامج ISE:

الأفعى تحمل نظرة:

==================================================== ========================

* التقرير الأخير *

==================================================== ========================

النتائج النهائية

اسم ملف إخراج المستوى الأعلى من RTL: adder_Carry_Look_ahead.ngr

اسم ملف إخراج المستوى الأعلى: adder_Carry_Look_ahead

تنسيق الإخراج: NGC

هدف التحسين: السرعة

الحفاظ على التسلسل الهرمي: لا

إحصائيات التصميم

عدد IOs: 98

استخدام الخلية:

# بيلس: 64

# LUT3: 64

# مخازن الإدخال والإخراج: 98

# IBUF: 65

# OBUF: 33

==================================================== ========================

ملخص استخدام الجهاز:

——————————

الجهاز المحدد: 3s50pq208-5

عدد الشرائح: 37 من 768 4٪

عدد 4 طوابق مدخلات: 64 من 1536 4٪

عدد IOs: 98

عدد IOBs المستعبدين: 98 من 124 79٪

——————————

ملخص موارد القسم:

——————————

لم يتم العثور على أقسام في هذا التصميم.

——————————

==================================================== ========================

تقرير التوقيت

ملاحظة: هذه الأرقام الزمنية هي فقط تقدير توليف.

للحصول على معلومات دقيقة عن التوقيت ، يرجى الرجوع إلى تقرير التتبع

تم إنشاؤه بعد المكان والطريق.

معلومات الساعة:

———————

لم يتم العثور على إشارات ساعة في هذا التصميم

معلومات إشارات التحكم غير المتزامنة:

——————————————-

لم يتم العثور على إشارات تحكم غير متزامنة في هذا التصميم

ملخص التوقيت:

—————

درجة السرعة: -5

أدنى فترة: لم يتم العثور على مسار

الحد الأدنى لوقت وصول الإدخال قبل الساعة: لم يتم العثور على مسار

أقصى وقت مطلوب للإخراج بعد الساعة: لم يتم العثور على مسار

أقصى تأخير للمسار التوافقي: 47.847 نانو ثانية

تفاصيل التوقيت:

————–

جميع القيم المعروضة بالنانو ثانية (ns)

==================================================== ========================

قيد التوقيت: تحليل المسار الافتراضي

إجمالي عدد المسارات / منافذ الوجهة: 1153/33

—————————————————————————-

التأخير: 47.847 نانو ثانية (مستويات المنطق = 34)

المصدر: x_in <0> (PAD)

الوجهة: مجموع <31> (PAD)

مسار البيانات: x_in <0> لمجموع <31>

بوابة نت

) الخلية: in-> out fanout Delay Delay Delay Logical Name (Net Name)

المضاعف:

==================================================== =============

* التقرير الأخير *

==================================================== ========================

النتائج النهائية

اسم ملف إخراج المستوى الأعلى من RTL: multiplier_unsigned.ngr

اسم ملف إخراج المستوى الأعلى: multiplier_unsigned

تنسيق الإخراج: NGC

هدف التحسين: السرعة

الحفاظ على التسلسل الهرمي: لا

إحصائيات التصميم

عدد IOs: 64

استخدام الخلية:

# بيلس: 1016

رقم GND: 1

# LUT1: 1

# LUT2: 30

# LUT3: 185

# LUT4: 291

# مكسي: 240

# MUXF5: 28

# XORCY: 240

# مخازن الإدخال والإخراج: 64

# IBUF: 32

# OBUF: 32

==================================================== =============

ملخص استخدام الجهاز:

——————————

الجهاز المحدد: 3s50pq208-5

عدد الشرائح: 270 من 768 35٪

عدد 4 طوابق مدخلات: 507 من 1536 33٪

عدد IOs: 64

عدد IOBs المستعبدين: 64 من 124 51٪

——————————

ملخص موارد القسم:

——————————

لم يتم العثور على أقسام في هذا التصميم.

——————————

==================================================== =============

تقرير التوقيت

ملاحظة: هذه الأرقام الزمنية هي فقط تقدير توليف.

للحصول على معلومات دقيقة عن التوقيت ، يرجى الرجوع إلى تقرير التتبع

تم إنشاؤه بعد المكان والطريق.

معلومات الساعة:

———————

لم يتم العثور على إشارات ساعة في هذا التصميم

معلومات إشارات التحكم غير المتزامنة:

——————————————-

لم يتم العثور على إشارات تحكم غير متزامنة في هذا التصميم

ملخص التوقيت:

—————

درجة السرعة: -5

أدنى فترة: لم يتم العثور على مسار

الحد الأدنى لوقت وصول الإدخال قبل الساعة: لم يتم العثور على مسار

أقصى وقت مطلوب للإخراج بعد الساعة: لم يتم العثور على مسار

الحد الأقصى لتأخير المسار التوافقي: 48.993 نانو ثانية

تفاصيل التوقيت:

————–

جميع القيم المعروضة بالنانو ثانية (ns)

==================================================== ========================

قيد التوقيت: تحليل المسار الافتراضي

إجمالي عدد المسارات / منافذ الوجهة: 134597834529761/32

—————————————————————————-

التأخير: 48.993 نانو ثانية (مستويات المنطق = 62)

المصدر: b_unsigned <0> (PAD)

الوجهة: mult_unsigned <30> (PAD)

مسار البيانات: b_unsigned <0> إلى mult_unsigned <30>

بوابة نت

الخلية: in-> out fanout Delay Delay Logical Name (Net Name)

مقسم:

==================================================== =============

* التقرير الأخير *

==================================================== =============

النتائج النهائية

اسم ملف إخراج المستوى الأعلى من RTL: n_Bit_Divider.ngr

اسم ملف إخراج المستوى الأعلى: n_Bit_Divider

تنسيق الإخراج: NGC

هدف التحسين: السرعة

الحفاظ على التسلسل الهرمي: لا

إحصائيات التصميم

عدد IOs: 64

استخدام الخلية:

# بيلس: 3044

رقم GND: 1

# INV: 46

# LUT2: 88

# LUT3: 496

# LUT4: 864

# MULT_AND: 57

# مكسي: 995

# VCC: 1

# XORCY: 496

# مخازن الإدخال والإخراج: 64

# IBUF: 32

# OBUF: 32

==================================================== =============

ملخص استخدام الجهاز:

—————————–

الجهاز المحدد: 3s50pq208-5

عدد الشرائح: 798 من 768103٪ (*)

عدد 4 طوابق مدخلات: 1494 من 1536 97٪

عدد IOs: 64

عدد IOBs المستعبدين: 64 من 124 51٪

تحذير: Xst: 1336 – (*) يتم استخدام أكثر من 100٪ من موارد الجهاز

——————————

ملخص موارد القسم:

——————————

لم يتم العثور على أقسام في هذا التصميم.

——————————

==================================================== ========================

تقرير التوقيت

ملاحظة: هذه الأرقام الزمنية هي فقط تقدير توليف.

للحصول على معلومات دقيقة عن التوقيت ، يرجى الرجوع إلى تقرير التتبع

تم إنشاؤه بعد المكان والطريق.

معلومات الساعة:

———————

لم يتم العثور على إشارات ساعة في هذا التصميم

معلومات إشارات التحكم غير المتزامنة:

——————————————-

لم يتم العثور على إشارات تحكم غير متزامنة في هذا التصميم

ملخص التوقيت:

—————

درجة السرعة: -5

أدنى فترة: لم يتم العثور على مسار

الحد الأدنى لوقت وصول الإدخال قبل الساعة: لم يتم العثور على مسار

أقصى وقت مطلوب للإخراج بعد الساعة: لم يتم العثور على مسار

أقصى تأخير للمسار التوافقي: 177.225ns

تفاصيل التوقيت:

————–

جميع القيم المعروضة بالنانو ثانية (ns)

==================================================== =============

قيد التوقيت: تحليل المسار الافتراضي

إجمالي عدد المسارات / منافذ الوجهة: 9302334276068681700000000000000000000000000000000000000/32

—————————————————————————-

التأخير: 177.225ns (مستويات المنطق = 536)

المصدر: y_in <0> (PAD)

الوجهة: frac <0> (PAD)

مسار البيانات: y_in <0> إلى frac <0>

بوابة نت

الخلية: in-> out fanout Delay Delay Logical Name (Net Name)

ALU:

==================================================== =============

* التقرير الأخير *

==================================================== =============

النتائج النهائية

اسم ملف إخراج المستوى الأعلى من RTL: ALU.ngr

اسم ملف إخراج المستوى الأعلى: ALU

تنسيق الإخراج: NGC

هدف التحسين: السرعة

الحفاظ على التسلسل الهرمي: لا

إحصائيات التصميم

عدد IOs: 60

استخدام الخلية:

# BELS: 1040

رقم GND: 1

# INV: 15

# LUT1: 1

# LUT2: 82

# LUT3: 164

# LUT4: 272

# MULT_AND: 25

# مكسي: 289

# MUXF5: 21

# VCC: 1

# XORCY: 169

# مخازن الإدخال والإخراج: 60

# IBUF: 19

# OBUF: 41

==================================================== =============

ملخص استخدام الجهاز:

——————————

الجهاز المحدد: 3s50pq208-5

عدد الشرائح: 289 من 768 37٪

عدد 4 طوابق مدخلات: 534 من 1536 34٪

عدد IOs: 60

عدد IOBs المستعبدين: 60 من 124 48٪

——————————

ملخص موارد القسم:

——————————

لم يتم العثور على أقسام في هذا التصميم.

——————————

==================================================== =============

تقرير التوقيت

ملاحظة: هذه الأرقام الزمنية هي فقط تقدير توليف.

للحصول على معلومات دقيقة عن التوقيت ، يرجى الرجوع إلى تقرير التتبع

تم إنشاؤه بعد المكان والطريق.

معلومات الساعة:

———————

لم يتم العثور على إشارات ساعة في هذا التصميم

معلومات إشارات التحكم غير المتزامنة:

——————————————-

لم يتم العثور على إشارات تحكم غير متزامنة في هذا التصميم

ملخص التوقيت:

—————

درجة السرعة: -5

أدنى فترة: لم يتم العثور على مسار

الحد الأدنى لوقت وصول الإدخال قبل الساعة: لم يتم العثور على مسار

أقصى وقت مطلوب للإخراج بعد الساعة: لم يتم العثور على مسار

الحد الأقصى لتأخير المسار التوافقي: 83.108ns

تفاصيل التوقيت:

————–

جميع القيم المعروضة بالنانو ثانية (ns)

==================================================== =============

قيد التوقيت: تحليل المسار الافتراضي

إجمالي عدد المسارات / منافذ الوجهة: 83353851265305404000000/41

—————————————————————————-

التأخير: 83.108ns (مستويات المنطق = 142)

المصدر: datain2 <5> (PAD)

الوجهة: frac <0> (PAD)

مسار البيانات: datain2 <5> إلى frac <0>

المراجعات

لا توجد مراجعات بعد.